Post place &route layout of Xilinx Virtex-4 FPGA slice generated from... | Download Scientific Diagram

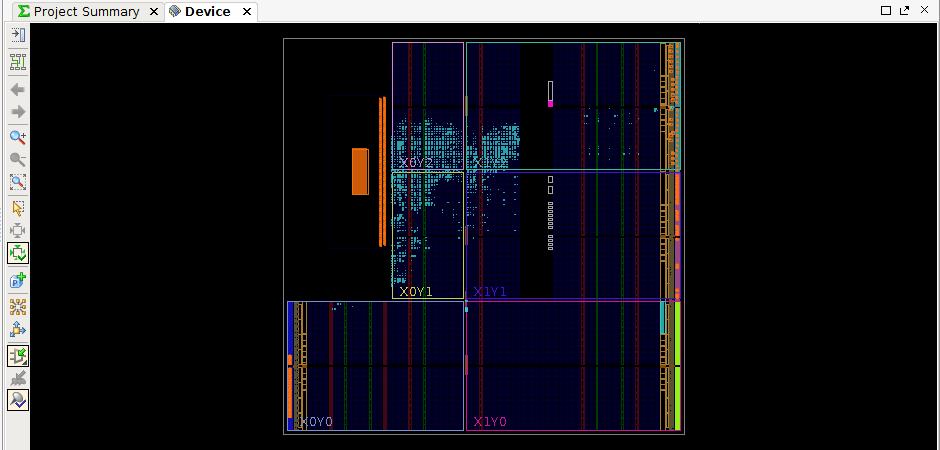

Place and route results for Bene s network with N = 8. Device: Xilinx... | Download Scientific Diagram

9: Timing report extracted from the Xilinx place-and-route results for... | Download Scientific Diagram